Le mur mémoire que la HBM4 repousse

Chaque modèle d’IA — de GPT-5.4 à Gemini 3.1 — se heurte au même goulot d’étranglement : le GPU peut calculer plus vite que la mémoire ne peut lui fournir des données. Ce « mur mémoire » signifie que les processeurs restent inactifs en attendant le prochain lot de poids et d’activations, gaspillant des milliards de dollars en silicium. En février 2026, Samsung a commencé à livrer la première HBM4 commerciale de l’industrie, offrant un bond générationnel en bande passante qui repousse significativement ce mur.

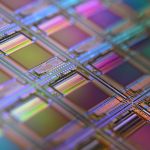

Construite sur le procédé DRAM 6e génération 10nm (1c) de Samsung, la HBM4 atteint des vitesses de transfert constantes de 11,7 Gbit/s par broche, avec une capacité allant jusqu’à 13 Gbit/s. Avec 2 048 broches d’E/S de données — le double des 1 024 de la HBM3E — une seule pile HBM4 délivre jusqu’à 3,3 To/s de bande passante, une amélioration de 2,7x par rapport à son prédécesseur.

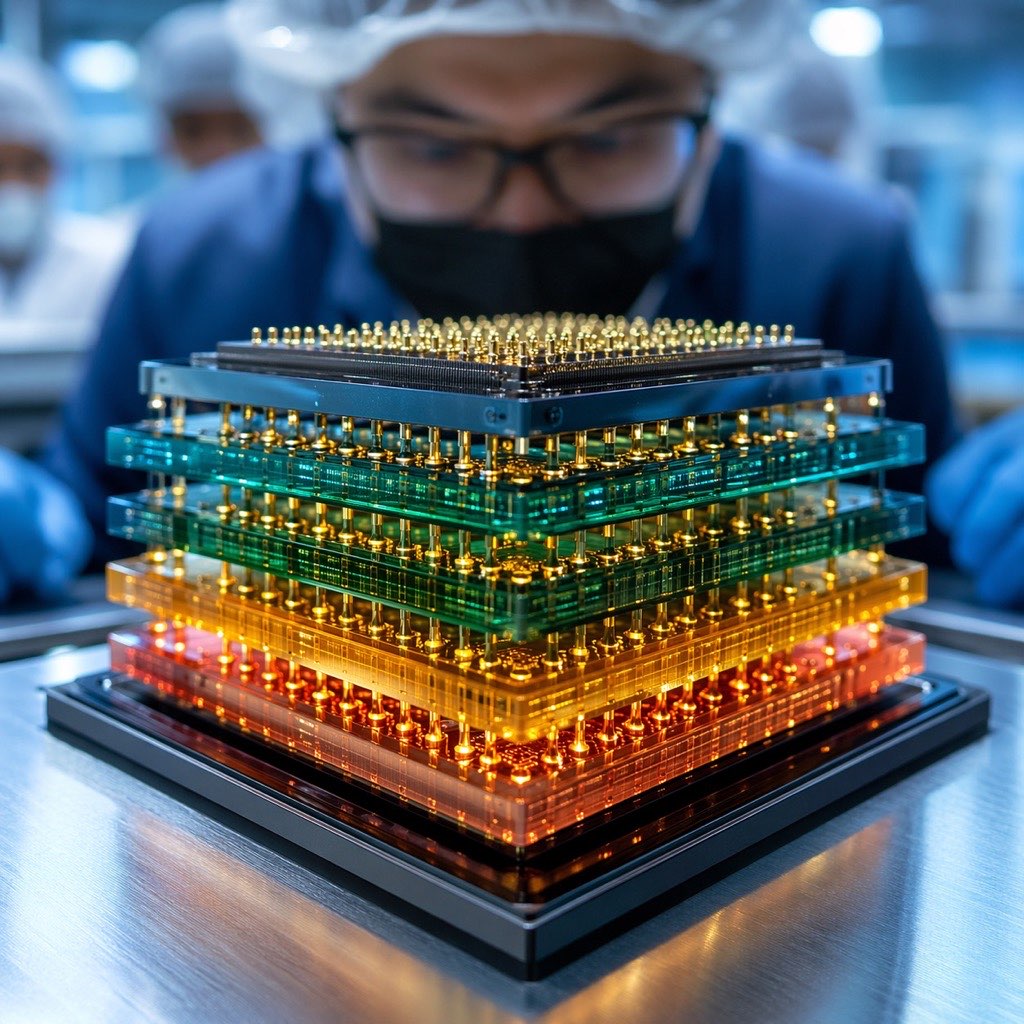

Empiler plus haut : de 36 Go à 48 Go

La gamme HBM4 actuelle de Samsung utilise la technologie d’empilement à 12 couches, offrant des capacités de 24 Go à 36 Go par pile. Mais la véritable cible de la feuille de route est l’empilement à 16 couches, qui poussera la capacité à 48 Go par pile. Pour contexte, le GPU actuel NVIDIA Blackwell B200 utilise des piles HBM3E de 24 Go chacune. Doubler cela à 48 Go par pile signifie que les modèles d’IA plus grands peuvent tenir entièrement dans la mémoire GPU sans la pénalité de performance du déchargement vers un stockage plus lent.

Le défi d’ingénierie est formidable. Chaque die DRAM doit être aminci à environ 30 micromètres avant l’empilement — plus fin qu’un cheveu humain — avec des milliers de vias traversant le silicium (TSV) connectant les couches verticalement. Les rendements DRAM 1c de Samsung tournent autour de 60 %, et les rendements effectifs chutent davantage après le traitement avancé back-end. La configuration à 16 couches amplifie ces défis, car tout défaut dans n’importe quelle couche peut rendre la pile entière inutilisable.

Publicité

Des gains d’efficacité au-delà de la vitesse brute

La vitesse n’est pas la seule amélioration. La HBM4 atteint une amélioration de 40 % de l’efficacité énergétique par rapport à la HBM3E grâce à la technologie TSV basse tension et l’optimisation du réseau de distribution d’énergie. La résistance thermique s’améliore de 10 % et la dissipation thermique de 30 %. Ces chiffres comptent car les piles HBM sont directement sur ou adjacentes au die GPU, où les températures dépassent régulièrement 100 degrés Celsius.

La course à trois pour les commandes de NVIDIA

La HBM4 est le terrain où Samsung, SK Hynix et Micron se disputent le plus intensément, car NVIDIA est effectivement le seul client qui compte à grande échelle. SK Hynix détient actuellement environ 70 % de l’allocation HBM4 de NVIDIA pour la prochaine plateforme Vera Rubin, Samsung captant environ 30 % — un retour significatif après avoir été largement exclu de l’approvisionnement HBM3E pour NVIDIA.

Samsung lutte agressivement pour combler l’écart. L’entreprise a passé les tests qualité de NVIDIA, lancé la production de masse sur son campus de Pyeongtaek, et projette que les ventes HBM tripleront en 2026 par rapport à 2025. Samsung a également établi un partenariat avec AMD pour des solutions de mémoire IA de nouvelle génération.

Samsung prévisualise déjà la prochaine génération. Au NVIDIA GTC 2026, l’entreprise a présenté la HBM4E, qui délivre 16 Gbit/s par broche et 4,0 To/s de bande passante par pile. L’échantillonnage de la HBM4E commence au second semestre 2026.

Pourquoi la HBM4 compte pour l’infrastructure IA

Le marché HBM connaît ce que les analystes appellent un « supercycle de la mémoire IA ». SK Hynix prévoit une croissance annuelle de 30 % de la HBM jusqu’en 2030, et la capacité HBM entière de Micron est épuisée jusqu’en 2026. Le déséquilibre offre-demande est si sévère que la production de GPU gaming a subi des coupes de 40 % alors que les fabricants de mémoire priorisent l’allocation aux puces IA.

Pour les entreprises construisant ou achetant de l’infrastructure IA, la HBM4 a des implications immédiates. Les entraînements qui nécessitaient auparavant des configurations multi-nœuds parce que les poids du modèle dépassaient la mémoire d’un seul GPU pourraient tenir sur moins de GPU avec des piles HBM4 de 48 Go. Les charges d’inférence en bénéficient encore plus : une bande passante plus élevée signifie une latence plus faible par token, affectant directement le coût et la vitesse de chaque appel API à chaque modèle d’IA.

Questions Fréquemment Posées

Qu’est-ce que la HBM4 et pourquoi est-elle importante pour l’IA ?

La HBM4 (High Bandwidth Memory 4e génération) est la dernière technologie mémoire conçue spécifiquement pour les accélérateurs IA. La HBM4 de Samsung délivre jusqu’à 3,3 To/s de bande passante par pile — 2,7 fois plus vite que la HBM3E — avec des capacités atteignant 48 Go grâce à un empilement à 16 couches. C’est important car les modèles d’IA sont de plus en plus limités par la bande passante mémoire plutôt que par la puissance de calcul, et la HBM4 répond directement à ce goulot.

Comment la HBM4 de Samsung se compare-t-elle à l’offre de SK Hynix ?

Samsung a livré la première HBM4 commerciale au monde en février 2026. Cependant, SK Hynix détient environ 70 % de l’allocation HBM4 de NVIDIA pour la plateforme Vera Rubin contre 30 % pour Samsung. Les deux entreprises font la course pour livrer des configurations à 16 couches, Samsung prévisualisant déjà la HBM4E (4,0 To/s) au GTC 2026. Micron est un concurrent plus lointain.

Quand le matériel IA sous HBM4 sera-t-il disponible en cloud ?

La plateforme NVIDIA Vera Rubin, qui utilise la mémoire HBM4, devrait être lancée au second semestre 2026. Les fournisseurs cloud ont généralement besoin de 3 à 6 mois après le lancement du GPU pour déployer à grande échelle, ce qui signifie que les instances cloud HBM4 devraient être disponibles début à mi-2027.